e-ISSN: 2319-8753 | p-ISSN: 2347-6710

DIA

## International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 13, Issue 3, March 2024

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

# Impact Factor: 8.423

9940 572 462

6381 907 438

$\bigcirc$

e-ISSN: 2319-8753, p-ISSN: 2347-6710 www.ijirset.com | Impact Factor: 8.423 A Monthly Peer Reviewed & Referred Journal |

Volume 13, Issue 3, March 2024

DOI:10.15680/IJIRSET.2024.1303183

# A Hybrid Topological Flip Flop Design for High Speed and Low Power Applications

J. Haritha<sup>1</sup>, B. Sravani<sup>2</sup>, G. Sada<sup>3</sup>, M. Velugonda Reddy<sup>4</sup>, M. Raghunath<sup>5</sup>

<sup>1</sup>Assistant Professor, Department of ECE, Annamacharya Institute of Technology & Sciences, Tirupati, India

<sup>2,3,4,5</sup>Students of ECE, Annamacharya Institute of Technology& Sciences, Tirupati, India

**ABSTRACT:** Flip-flops are essential parts of digital circuits used to store state data. It is crucial to decrease their power consumption, latency, and area in order to fulfil performance requirements. This study describes a hybrid flip-flop device with eighteen transistors that combines static CMOS logic with pass transistors. It resolves the issue of clock overloading that plagues traditional designs. The hybrid technique makes it possible to achieve the three main goals for flip-flops: high speed, low power consumption, and small size. The proposed circuit is implemented using Tanner Tools and compared with the Transmission gate flip-flopThe hybrid logic architecture that has been suggested has demonstrated the greatest power improvement that is, 19.9µWwhen compared to TGFF.

KEYWORDS - CMOS, low power, flip-flop, complementary pass transistor.

#### **I.INTRODUCTION**

A flip-flop is a basic storage element that is frequently utilised in digital system designs. In low power electronics applications like smartphones, tablets, mobile phones, and other handheld devices, the flip-flop is widely employed. For a while every gadget should have a long battery life and little power consumption. Memory unit latency should also be kept to a minimum for quick processing performance. The clock system in digital hardware circuits accounts for 20% to 40% of the integrated circuit's (IC) overall power consumption. Through the use of several low power approaches, flip-flop designs are continuously improved. The most popular industry standard flip-flop is the Transmission Gate flip-flop (TGFF). Clock overloading is the main issue with these designs. These flip-flop logic structures are made up of the CLK and CLK bar clock signals, respectively. These signals raise the number of transistors in addition to increasing the clock signal's workload. Because more circuitry is needed to generate the CLK and CLK bar signals, there are changes to the overall design structure. This resulted in a notable rise in dynamic power losses, even during periods of low data switching activity. These days, the two main issues for VLSIs are production costs and chip area.

This brief describes the design of a flip-flop using hybrid logic. In comparison to the current M-S flip-flops, the suggested flip-flop structure tackles the notable improvement in (1) Clock to Q delay. (2) This work also avoids clock overloading, which contributes to a lower power usage. (3) A decrease in the number of PMOS transistors, which lowers the circuit's total power, area, and latency. Reducing the total intricacy. All of the results were obtained using Tanner tools at room temperature and 250nm UMC CMOS technology with a maximum supply voltage of 0.5 V.

#### **II.EXISTING METHOD**

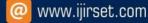

inverters TGFF. Transmission gates and make up the А master-slave setup is used. Two transmission gates operated by an inverted clock and a clock that is attached to the input data line make up the master latch. These enable the input data to be sampled by the master on the clock's rising edge. when the clock is low, the two inverters that the master drives maintain the state. Transmission gates are also used by the slave latch to collect the master output when the clock's falling edge occurs. The ultimate output inverter is powered by the slave. The fact that 12 transistors are clocked results in significant clock loading, and contention current occurs when both transmission gates are partially on during transitions.

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

#### Volume 13, Issue 3, March 2024

DOI:10.15680/IJIRSET.2024.1303183

FIGURE 1:BLOCK DIAGRAM OF TGFF

## III. PROPOSED FLIP-FLOP DESIGN

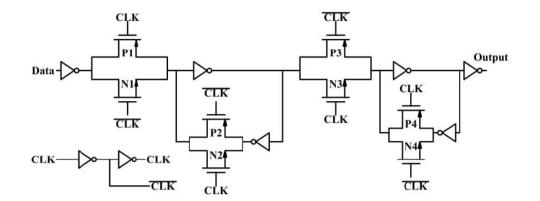

In order to minimise latency, minimise circuit complexity, and optimise power consumption, we have logically and topologically decreased the number of transistors, particularly PMOS transistors. We have reduced the continuous 2 PMOS transistors in the same path from VDD to GND because of the limited mobility of the PMOS transistors. As a result, the proposed flip-flop has less delay Furthermore, because the suggested design has a simpler circuit than the LRFF, it takes up less space. Our suggested design, known as a hybrid flip-flop (HFF), is seen in Figure. Since it also includes a balancing clock and logic reduction.LRFF and ACFF are both included in the suggested hybrid construction, which satisfies the specifications with just 18 transistors. Four pass transistors (P2, P3, N6, and N7), two NMOS to store data in master transistors, and six inverters make up the hybrid topological structure. Of the four pass transistors, one pair acts as an auxiliary transistor (AT) to provide either a strong 1 or a weak 0. The other pass transistor pair functions as a current booster (CB).

e-ISSN: 2319-8753, p-ISSN: 2347-6710 www.ijirset.com | Impact Factor: 8.423 | A Monthly Peer Reviewed & Referred Journal |

#### Volume 13, Issue 3, March 2024

#### DOI:10.15680/IJIRSET.2024.1303183

FIGURE 2: BLOCK DIAGRAM OF PROPOSED METHOD

DESIGN OF PROPOSED METHOD

#### A.Cases of Data Latching

1)Situation (Clock = 0 and Data = 0): Node "u1" equals 1 when CLK = 0 and DATA = 0, so P1, P2, and N4 transistors will be in the ON state. However, since transistors N6 and N7 are off, neither the "master" node nor node u2 will be able to send any data to the slave latch. Slave will therefore retain its prior value at the output node. Transistor P3 acts as an AT in this situation since it passes weak 0 at the "master" node. Since the transistor P2 passes a strong 1 that satisfies the logic 0 at the master node, it acts as a current booster.

2) Case (Data = 0 and Clock = 1): Transistors N6 and N7 will be in the ON state when CLK = 1 and DATA = 0. Slave nodes "a" and "b" receive data from the "master" and "u2" nodes via N6 and N7, respectively. This uses the slave to supply the data at the output. N6 is a CB when the master node output is 0 because it passes strong "0" at node "a." N7 is an AT at the same time since it passes weak "1" at node "b"

3)Case (Data = 1 and Clock = 0): transistors N1, P2, and P4 will be in the ON state when CLK = 0 and DATA = 1. This causes node u1 and u2 to be pulled to logic "0," but the master node keeps the data at logic "1." At the output node, the slave will retain the value it had before. Transistor P2 acts as an AT under these circumstances, passing weak 0 at node u1. Transistor P3, on the other hand, acts like a CB since it passes strong 1 at the master node.

4) Situation (Clock = 1) and Data = 1): Similarto the example above where CLK = 1, logic at the master node will be passed to the slave when CLK = 1 and DATA = 1. N7 acts as a CB when the master node output is at logic "1," passing strong "0" at node "b" N6 acts like an AT at the same time since it passes weak "1" at node "a."

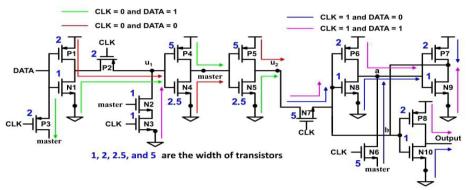

#### **IV. EXPERIMENTAL RESULTS**

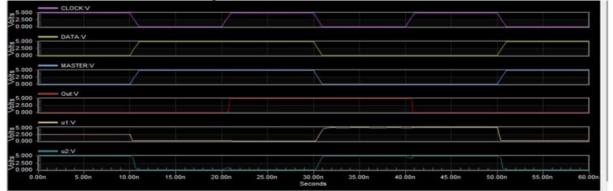

#### A.Output Waveform

Clock, Data and Master are the inputs, clock and data are the primary inputs and master behave as input to transfer the data to slave. Here when CLK=0, DATA=0 and MASTER =1, no data will be transferred. when CLK =1, DATA =1

e-ISSN: 2319-8753, p-ISSN: 2347-6710 www.ijirset.com | Impact Factor: 8.423 A Monthly Peer Reviewed & Referred Journal |

### Volume 13, Issue 3, March 2024

DOI:10.15680/IJIRSET.2024.1303183

andMASTER =0,data will not transferred to slave node but data will be hold. when CLK =1,DATA =1 and MASTER =1, data will transferred to slave node through master node.

#### **B.**Power, Area and Delay

| PARAMETERS  | TGFF      | HFF      |

|-------------|-----------|----------|

|             |           |          |

| Power       | 20.90(µW) | 1.00(µW) |

| Transistors | 22        | 18       |

| Delay       | 0.88sec   | 0.52sec  |

HFF turns out to be the most practical and efficient option when TGFF and HFF are compared across power, area, and delay factors, according to the data presented. With a power consumption of only  $1.00\mu$ W as opposed to TGFF's  $20.90\mu$ W, it offers superior energy efficiency. Furthermore, HFF takes up less space (18 units) than TGFF (22 units), indicating a more compact design that is beneficial for lowering production costs and enhancing device integration. In addition, HFF performs better than TGFF with a delay time, which makes it speedier and more appropriate for situations where speed is crucial. Overall, HFF is a better choice for a variety of applications due to its smaller size, quickerprocessing, and reduced power consumption.

#### C. Variation of Power With Supply Voltage

Figure shows the power consumption level at various supply voltages between 0.5 V and 1 V. Among state-of-the-art work, the HFF has the lowest power consumption and functions correctly at this voltage range. This is because there are fewer transistors on the critical path of the suggested flip-flop. This is accomplished by eliminating PMOS from the circuit without compromising its operation.

#### **V.CONCLUSION**

The design of a new flip-flop made with Eighteen transistors. The following criteria have been taken into consideration for the proposed work: C to Q latency, reduction in PMOS transistor count, reduced circuit complexity, and absence of clock overloading. In comparison to TGFF, the HFF circuit performed better in terms of powerconsumption by  $1.02\mu$ Wrespectively. It performs exceptionally well across the supply voltages and is free from clock overloading. Every parameter that was used for this task has been effectively addressed. The proposed method and power consumption isdecreased by  $19.90\mu$ W.

#### REFERENCES

1.Alok Kumar Mishra, Urvashi Chopra, and D. Vaithiyanathan "A Partially Static High Frequency 18T Hybrid Topological Flip-Flop Design for Low Power Application", 1549-7747, 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

2. F. Stas and D. Bol, "A 0.4-V 0.66-fJ/cycle retentive true-single-phase-clock 18 T flip-flop in 28-nm fully-depleted SOI CMOS", IEEE Trans. Circuits Syst. I Reg. Papers, vol. 65, no. 3, pp. 935-945, Mar. 2018.

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

### Volume 13, Issue 3, March 2024

#### DOI:10.15680/IJIRSET.2024.1303183

3.Kim, Y.; Shin, B. A static contention-free single-phase-clocked 24T flip-flop in 45nm for low-power applications. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 466–467.

4.Stas, F.; Bol, D. A 0.4-V 0.66-fJ/cycle retentive true-single-phase clock 18T flip-flop in 28-nm fully-depleted SOI CMOS. IEEE Trans. Circuits Syst. I Reg. Pap. 2018, 65, 935–945.

5. Kawai, N.; Ishinura, M. A fully static topologically-compressed 21-transistor flip-flop with 75% power saving. IEEE J. Solid-State Circuits 2014, 49, 2526–2533

6. Kuamar, H.; Nagarajan, R. Low Power High Speed 15-Transistor Static True Single Phase Flip Flop. In Proceedings of the 2nd International Conference on Intelligent Computing, Instrumentation and Control Technologies (ICICICT), Kannur, India, 5–6 July 2019; pp. 440–444

7. Lin, J.F.; Sheu, M.H.; Hwang, Y.T.; Wong, C.S.; Tsai, M.Y. Low-power 19-transistor true single-phase clocking flipflop design based on logic structure reduction schemes. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 3033– 3044.

8. Lin, J.-F.; Hong, Z.-J.; Tsai, C.-M.; Wu, B.-C.; Yu, S.-W. Novel "Low-Complexity and Low-Power Flip-Flop Design". Electronics 2020, 9, 783.

9. Shin, G.; Lee, E.; Lee, J.; Lee, Y.; Lee, Y. An ultra-low-power fully-static contention-free flip-flop with complete redundant clock transition and transistor elimination. IEEE J. Solid-State Circuits 2021, 56, 3039–3048.

10. Y. Cai, A. Savanth, P. Prabhat, J. Myers, A. S. Weddell and T. Kazmierski, "Evaluation and analysis of single-phase clock flip-flops for NTV applications", Proc. 27th Int. Symp. Power Timing Modeling Optim. Simulation (PATMOS), pp. 1-6, Sep. 2017.

11. C. K. Teh, T. Fujita, H. Hara and M. Hamada, "A 77% energy-saving 22-transistor single-phase-clocking D-flipflop with adaptive-coupling configuration in 40 nm CMOS", IEEE ISSCC Dig. Tech. Papers, pp. 338-340, Feb. 2011 12.Yang, B.-D. Low-Power and Area-Efficient Shift Register Using Pulsed Latches. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1564–1571

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com